Introduction to High-speed PCB Design

High-speed printed circuit board (PCB) design refers to the specialized design techniques used for circuits that operate at high frequencies or have fast edge rates. As digital systems push the boundaries of speed and bandwidth, high-speed design considerations become increasingly important to ensure signal integrity, minimize noise, and avoid electromagnetic interference (EMI) issues.

Proper high-speed PCB design is critical for applications such as high-speed digital interfaces, RF and microwave circuits, and high-performance computing systems. Without careful design, high-speed signals can suffer from degradation, cross-talk, reflections, and other problems that can compromise system performance and reliability.

Some key challenges in high-speed PCB design include:

-

Managing signal integrity: As frequencies increase, PCB traces start to behave more like transmission lines and are susceptible to reflections, attenuation, and distortion. Proper impedance matching, termination, and routing techniques are necessary to maintain clean signals.

-

Minimizing EMI: High-speed circuits can generate significant electromagnetic radiation that can interfere with nearby circuits or violate regulatory limits. Careful PCB layout, shielding, and filtering are needed to minimize EMI.

-

Controlling power integrity: High-speed ICs have demanding power requirements and are sensitive to voltage fluctuations. Robust power distribution networks with low impedance and minimal noise are essential.

-

Dealing with high density: To keep up with increasing pin counts and shrinking packages, high-speed PCBs often have very fine pitch traces and high layer counts. This requires advanced manufacturing capabilities and meticulous design for manufacturability.

Successful high-speed PCB design requires a combination of specialized knowledge, tools, and techniques. In the following sections, we’ll explore four key areas that are very helpful for designing high-speed PCBs.

1. Impedance Control and Matching

One of the most fundamental aspects of high-speed PCB design is managing the characteristic impedance of transmission lines. When a signal encounters an impedance discontinuity, such as a change in trace width or a connector, a portion of the signal energy is reflected back to the source. These reflections can cause ringing, overshoot, undershoot, and other signal integrity problems.

To minimize reflections and ensure clean signal propagation, the characteristic impedance of PCB traces must be carefully controlled to match the impedance of the source and load. Some common techniques for impedance control include:

Controlled Impedance Traces

The characteristic impedance of a PCB trace depends on its geometry (width, thickness, and spacing) and the properties of the surrounding dielectric material. By carefully choosing these parameters, PCB designers can create traces with a specific target impedance, such as 50Ω or 100Ω.

Controlled impedance traces are typically used for critical high-speed signals such as clocks, data buses, and RF lines. The PCB fabricator must tightly control the manufacturing process to maintain the specified impedance within tolerance.

Differential Pairs

Differential signaling, where a signal is transmitted as a pair of complementary traces with equal and opposite polarity, is commonly used in high-speed interfaces such as USB, PCIe, and Ethernet. Differential pairs offer several advantages over single-ended traces, including better noise immunity, lower EMI, and higher bandwidth.

To maintain the benefits of differential signaling, the two traces in a differential pair must be carefully matched in length, spacing, and impedance. Any mismatch can cause Mode Conversion, where some of the differential signal energy is converted into common-mode noise.

Terminations

Even with controlled impedance traces, reflections can still occur at the endpoints of a transmission line, such as at a receiver input or a connector. To minimize these reflections, termination techniques are used to match the impedance of the trace to the impedance of the load.

Some common termination schemes include:

-

Series termination: A resistor is placed in series with the driver output to match the trace impedance. This is simple and effective for point-to-point connections.

-

Parallel termination: A resistor is placed in parallel with the receiver input to match the trace impedance. This is commonly used for multi-drop buses.

-

AC termination: A series resistor and shunt capacitor are used to provide a high-frequency termination while allowing DC bias. This is often used for analog circuits.

The choice of termination depends on factors such as the signal type, trace length, and driver characteristics. Proper termination is critical for maintaining signal integrity and preventing reflections.

Impedance Discontinuities

Even with controlled impedance traces and proper termination, impedance discontinuities can still occur at various points along a transmission line. Some common sources of discontinuities include:

-

Vias: The change in geometry and dielectric constant at a via can cause an impedance mismatch. Techniques such as using smaller vias, matching via impedance to the trace, and using via stitching can help minimize the impact.

-

Connectors: The transition from a PCB trace to a connector can introduce a significant impedance discontinuity. Careful connector selection and PCB layout techniques, such as maintaining a constant impedance through the connector footprint, can help mitigate this.

-

Stubs: Unterminated branches off a main trace, such as those created by test points or unconnected pins, can act as stubs and cause reflections. Minimizing stub lengths and using stub termination techniques can help reduce their impact.

Managing impedance discontinuities requires a combination of careful PCB layout, component selection, and simulation. Tools such as time-domain reflectometry (TDR) and 3D electromagnetic simulation can help identify and optimize impedance discontinuities.

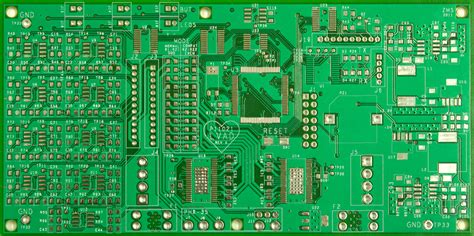

2. PCB stack-up and Materials

The choice of PCB materials and the arrangement of copper and dielectric layers, known as the stack-up, play a critical role in high-speed PCB design. The stack-up determines the impedance of the traces, the propagation velocity of signals, and the overall EMI and thermal performance of the board.

Dielectric Materials

The dielectric material, which separates the copper layers in a PCB, is characterized by its dielectric constant (Dk) and loss tangent (Df). The dielectric constant determines the capacitance between traces and the speed of signal propagation, while the loss tangent determines the amount of signal attenuation.

For high-speed designs, low-loss dielectrics with stable Dk and low Df are preferred to minimize signal attenuation and maintain consistent impedance. Some common high-speed dielectrics include:

- Rogers RO4000 series: A hydrocarbon ceramic laminate with low Dk and Df, suitable for RF and microwave applications.

- Isola IS410: A low-loss, high-speed laminate with low Dk and Df, suitable for data rates up to 25 Gbps.

- Nelco N4000-13SI: A low-loss, high-speed laminate with low Dk and Df, suitable for data rates up to 56 Gbps.

The choice of dielectric material depends on factors such as the operating frequency, data rate, cost, and manufacturability. In some cases, a combination of different dielectrics may be used in a hybrid stack-up to optimize performance and cost.

Copper Weigh and Roughness

The thickness and surface roughness of the copper layers in a PCB also affect high-speed performance. Thicker copper, typically specified in ounces per square foot (oz/ft²), reduces trace resistance and improves power handling, but can also increase capacitance and limit the minimum trace width and spacing.

Surface roughness, which is determined by the copper foil type and PCB manufacturing process, affects the Skin Effect resistance of traces at high frequencies. Rougher copper surfaces have higher skin effect losses, which can increase signal attenuation and limit bandwidth.

For high-speed designs, smoother copper foils, such as very low profile (VLP) or hyper very low profile (HVLP), are often used to minimize skin effect losses. The trade-off is that smoother foils can be more expensive and may have lower adhesion to the dielectric material.

Stack-up Design

The arrangement of copper and dielectric layers in a PCB stack-up determines the impedance and coupling of traces, as well as the overall thickness and manufacturability of the board. Some common stack-up considerations for high-speed designs include:

-

Symmetry: A symmetrical stack-up, with equal numbers of layers and identical materials on either side of the center line, helps prevent warpage and improves manufacturability.

-

Plane layers: Solid copper planes, such as power and ground planes, provide low-impedance reference planes for high-speed traces and help reduce EMI. Placing high-speed traces close to their reference planes minimizes loop area and reduces inductance.

-

Shielding layers: Placing additional ground layers between high-speed and sensitive traces can provide shielding and reduce cross-talk.

-

Dielectric thickness: Thinner dielectrics reduce the spacing between traces and planes, which can improve coupling and reduce EMI. However, thinner dielectrics also increase capacitance and reduce impedance, which may require narrower traces or more careful spacing.

Designing an optimal stack-up requires balancing the electrical requirements with the mechanical and manufacturing constraints. Tools such as Impedance Calculators and 2D field solvers can help optimize the stack-up for high-speed performance.

3. Power Distribution Network

The power distribution network (PDN) is a critical component of high-speed PCB design, as it provides the stable and clean power supply that high-speed ICs require for proper operation. A well-designed PDN ensures that the power supply voltage remains within the specified tolerance at all times, even in the presence of fast transient currents and noise.

Power Plane Design

The foundation of a robust PDN is a low-impedance power plane that provides a stable reference voltage for high-speed traces and components. The power plane should be designed to minimize impedance and voltage fluctuations across the frequency range of interest.

Some key considerations for power plane design include:

-

Placement: The power plane should be placed as close as possible to the high-speed components and traces that it supplies to minimize inductance and voltage drops.

-

Segmentation: In some cases, it may be necessary to split the power plane into multiple segments to isolate noisy or sensitive circuits. Care must be taken to ensure that the segments are properly decoupled and that return currents are not disrupted.

-

Cutouts: Cutouts in the power plane, such as for mounting holes or connectors, can increase impedance and cause voltage fluctuations. Minimizing cutouts and placing stitching vias around their perimeter can help reduce their impact.

-

Via placement: The placement and size of power vias, which connect the power plane to the surface components, can affect the impedance and current carrying capacity of the PDN. Placing vias close to the component power pins and using larger or multiple vias can help reduce impedance.

Simulating the impedance and voltage distribution of the power plane using tools such as 2D and 3D electromagnetic solvers can help optimize the design for high-speed performance.

Decoupling Capacitors

Decoupling capacitors are used to provide a local source of charge for fast transient currents and to filter high-frequency noise on the power supply. Properly selecting and placing decoupling capacitors is critical for maintaining a stable and clean PDN.

Some key considerations for decoupling capacitor selection and placement include:

-

Value and type: The capacitor value and type (e.g. ceramic, tantalum, aluminum) should be chosen to provide a low impedance path across the frequency range of interest. A combination of bulk, mid-frequency, and high-frequency capacitors is often used to cover a wide frequency range.

-

Placement: Decoupling capacitors should be placed as close as possible to the power pins of the components they are decoupling to minimize inductance. Placing capacitors on the same layer as the component and using short, wide traces can help reduce inductance.

-

Mounting: The mounting technique (e.g. surface mount, embedded) and pad geometry can affect the effective impedance of the capacitor. Using larger pads and minimizing the loop area between the capacitor and the power/ground planes can help reduce impedance.

-

Resonance: The interaction between the capacitor and the PDN can create resonances that can amplify noise at certain frequencies. Careful selection of capacitor values and placement, as well as the use of damping resistors or Ferrite beads, can help mitigate resonances.

Simulating the PDN impedance and transfer function using tools such as SPICE or specialized PDN analyzers can help optimize the decoupling strategy for high-speed performance.

Power Integrity Analysis

Power integrity analysis is the process of verifying that the PDN meets the voltage tolerance and noise requirements of the high-speed components across the frequency range of interest. This involves simulating the PDN impedance, voltage distribution, and transient response using models of the power planes, decoupling capacitors, and component loads.

Some key aspects of power integrity analysis include:

-

Target impedance: The target impedance of the PDN is determined by the voltage tolerance and current draw of the components. A common rule of thumb is to keep the PDN impedance below 1Ω up to the knee frequency of the fastest component.

-

Frequency domain analysis: Simulating the PDN impedance versus frequency can help identify resonances, anti-resonances, and impedance peaks that may cause voltage fluctuations or noise.

-

Time domain analysis: Simulating the PDN transient response to fast current steps can help verify that the voltage remains within tolerance during worst-case switching events.

-

Sensitivity analysis: Varying the component values, placement, and mounting in the simulation can help identify the most critical design parameters and optimize the PDN for robustness.

Power integrity analysis requires accurate models of the PDN components, including the power planes, decoupling capacitors, and IC packages. Tools such as vector network analyzers (VNAs) and TDR can be used to measure the actual impedance of the PDN components and verify the simulation models.

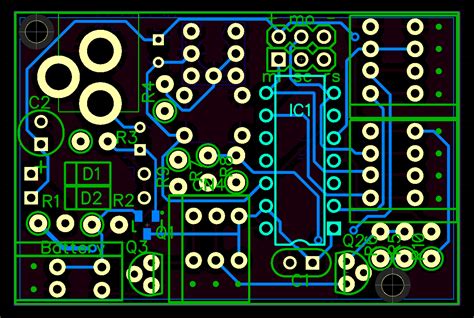

4. Layout and Routing

The physical layout and routing of high-speed traces on a PCB is a critical factor in determining the signal integrity, EMI, and overall performance of the design. Proper layout and routing techniques can help minimize cross-talk, reflections, and other signal degradation effects, while poor layout can lead to excessive noise, ringing, and even complete signal failure.

General Routing Guidelines

Some general guidelines for routing high-speed traces include:

-

Minimize trace length: Shorter traces have lower impedance, less delay, and are less susceptible to noise and reflections. Placing components close together and using direct routing paths can help minimize trace length.

-

Avoid sharp corners: Sharp corners in traces can cause impedance discontinuities and reflections. Using 45-degree angles or smooth curves instead of 90-degree corners can help maintain consistent impedance.

-

Maintain consistent spacing: Maintaining consistent spacing between traces and reference planes helps maintain consistent impedance and reduces cross-talk. Using autorouting tools with rule-based spacing constraints can help ensure consistent spacing.

-

Avoid crossing splits: Crossing a split in a reference plane, such as a gap or slot, can cause a return path discontinuity and lead to EMI and signal integrity problems. If a trace must cross a split, placing a stitching capacitor or return path bridge can help maintain continuity.

-

Use ground shielding: Placing a ground trace or plane adjacent to a high-speed trace can provide shielding and reduce cross-talk. The shielding should be placed as close as possible to the high-speed trace and connected to the reference plane with frequent vias.

Differential Pair Routing

Differential pairs require special consideration in routing to maintain the benefits of differential signaling. Some key guidelines for differential pair routing include:

-

Match length: The two traces in a differential pair should be matched in length to within a small tolerance, typically a few mils. This helps maintain a constant phase relationship between the signals and minimizes skew.

-

Maintain spacing: The spacing between the traces in a differential pair should be maintained as consistently as possible along the entire length of the pair. Any variation in spacing can cause impedance mismatch and mode conversion.

-

Use coupling: Placing the traces in a differential pair close together with tight coupling helps reject common-mode noise and reduces the loop area for EMI. The optimal spacing depends on the dielectric thickness and the desired impedance.

-

Avoid uncoupled sections: Any section of a differential pair where the traces are not coupled, such as at a via or connector, can cause mode conversion and reflections. Minimizing the length of uncoupled sections and using symmetrical routing can help reduce their impact.

Length Matching and Timing

In high-speed designs, the timing relationship between signals is critical for proper operation. Signals that arrive at their destination at different times can cause setup and hold violations, leading to data errors or even complete signal failure.

To ensure proper timing, high-speed traces must be carefully length matched and tuned to meet the timing constraints of the components. Some key considerations for length matching and timing include:

-

Skew: The difference in arrival time between related signals, such as clock and data or differential pairs, is called skew. Skew can be caused by differences in trace length, velocity, or delay. Minimizing skew through careful length matching and delay tuning is critical for high-speed performance.

-

Meandering: Adding intentional meandering or serpentine sections to a trace can help match its length to other traces in a group. However, excessive meandering can cause impedance discontinuities and reflections, so it should be used sparingly and with care.

-

Delay lines: In some cases, it may be necessary to add dedicated delay lines, such as serpentine traces or lumped element delay circuits, to a signal to

No responses yet