Introduction

In the world of printed circuit board (PCB) manufacturing, surface finishes play a crucial role in ensuring the reliability and longevity of the final product. One of the most popular surface finishes is the chemical Nickel-Gold (ENIG) finish, which offers excellent solderability, corrosion resistance, and a flat surface for fine-pitch components. However, when it comes to applying soldermask on via-holes in conjunction with ENIG, there are several considerations and challenges that need to be addressed.

This article will delve into the intricacies of applying soldermask on via-holes when using the chemical Nickel-Gold surface finish. We will explore the benefits and drawbacks of various approaches, discuss the technical aspects of the process, and provide insights into best practices for achieving optimal results.

What is a via-hole?

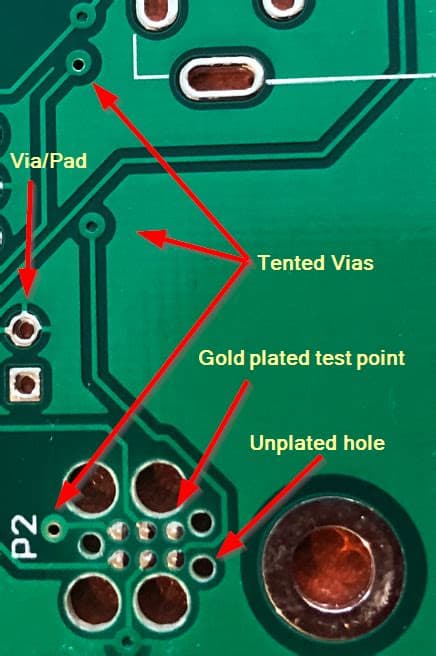

Before we dive into the specifics of soldermask application on via-holes, let’s first define what a via-hole is. In PCB design, a via-hole, or simply a via, is a small hole drilled through the board to establish an electrical connection between different layers of the PCB. Vias are essential for creating complex multi-layer PCB designs, as they allow signals to travel from one layer to another without interfering with other traces on the board.

There are several types of vias, including:

- Through-hole vias: These vias go through the entire thickness of the PCB, connecting all layers.

- Blind vias: These vias start from either the top or bottom layer and terminate at an inner layer, without going through the entire board.

- Buried vias: These vias connect two or more inner layers without reaching the top or bottom layer of the PCB.

The importance of soldermask on via-holes

Soldermask, also known as solder resist, is a thin layer of polymer applied to the surface of a PCB to protect the copper traces from oxidation and prevent solder bridging during the assembly process. When it comes to via-holes, applying soldermask can offer several benefits:

- Protection: Soldermask on via-holes helps protect the exposed copper from oxidation and contamination, which can lead to poor solderability and decreased reliability.

- Solder control: By covering the via-holes with soldermask, you can prevent solder from wicking into the vias during the reflow process, which can cause issues like solder starved joints or excessive solder consumption.

- Electrical isolation: Soldermask on via-holes helps maintain electrical isolation between adjacent vias, preventing short circuits and signal integrity issues.

Challenges of applying soldermask on via-holes with ENIG

While applying soldermask on via-holes offers several benefits, it also presents some challenges, particularly when using the chemical Nickel-Gold surface finish. Some of these challenges include:

-

Adhesion issues: The smooth, non-porous surface of the ENIG finish can make it difficult for the soldermask to adhere properly to the via-holes. This can lead to peeling or flaking of the soldermask, exposing the underlying copper and compromising the protection and reliability of the PCB.

-

Uneven coverage: Due to the small size and high aspect ratio of via-holes, achieving even and consistent soldermask coverage can be challenging. Uneven coverage can result in areas of exposed copper, which are susceptible to oxidation and contamination.

-

Compatibility with ENIG process: The chemicals used in the ENIG process, particularly the electroless nickel plating solution, can interact with the soldermask and cause issues like discoloration, blistering, or delamination. Ensuring compatibility between the soldermask and the ENIG process is crucial for achieving optimal results.

Approaches to applying soldermask on via-holes with ENIG

There are several approaches to applying soldermask on via-holes when using the chemical Nickel-Gold surface finish, each with its own advantages and disadvantages. Let’s explore some of these methods:

1. Tenting vias

Via tenting is a common method for applying soldermask on via-holes. In this approach, the soldermask is applied over the entire surface of the PCB, covering both the copper traces and the via-holes. The soldermask is then patterned and developed, leaving a thin layer of soldermask covering the via-holes.

Advantages:

– Provides complete coverage and protection of the via-holes

– Prevents solder from wicking into the vias during assembly

– Relatively simple and cost-effective process

Disadvantages:

– Can lead to air entrapment in the vias, causing reliability issues

– May result in uneven soldermask thickness over the vias

– Potential for soldermask cracking or peeling due to thermal stress

2. Plugging vias

Via plugging involves filling the via-holes with a non-conductive material, such as epoxy or resin, before applying the soldermask. This method creates a smooth, level surface for the soldermask to adhere to, improving coverage and adhesion.

Advantages:

– Eliminates air entrapment issues

– Provides a stable base for soldermask adhesion

– Allows for better control of soldermask thickness over the vias

Disadvantages:

– Requires an additional process step, increasing manufacturing time and cost

– Potential for incompatibility between the plugging material and the ENIG process

– May affect the electrical characteristics of the vias

3. Selective via capping

Selective via capping is a process where a thin layer of copper is electroplated over the via-holes before applying the soldermask. This copper cap seals the via-holes and provides a surface for the soldermask to adhere to.

Advantages:

– Eliminates the need for plugging materials

– Provides a conductive surface for soldermask adhesion

– Allows for better control of soldermask thickness over the vias

Disadvantages:

– Requires specialized equipment and processes

– May increase manufacturing time and cost

– Potential for compatibility issues with the ENIG process

Best practices for applying soldermask on via-holes with ENIG

To achieve optimal results when applying soldermask on via-holes in conjunction with the chemical Nickel-Gold surface finish, consider the following best practices:

-

Choose a soldermask with good adhesion properties and compatibility with the ENIG process. Work closely with your PCB manufacturer and soldermask supplier to select the best material for your application.

-

Ensure proper surface preparation before applying the soldermask. This may include cleaning, roughening, or plasma treatment to improve adhesion.

-

Use a soldermask application method that provides even and consistent coverage over the via-holes, such as electrospray or curtain coating.

-

Optimize the soldermask curing process to minimize thermal stress and ensure proper cross-linking of the polymer.

-

Conduct thorough testing and inspection to verify the quality and reliability of the soldermask coverage on the via-holes.

FAQ

-

Q: Can soldermask be applied on via-holes with other surface finishes besides ENIG?

A: Yes, soldermask can be applied on via-holes with other surface finishes, such as Immersion Silver (ImmAg), Organic Solderability Preservative (OSP), and Hot Air Solder Leveling (HASL). However, each surface finish has its own unique challenges and considerations when it comes to soldermask application. -

Q: Is via tenting or via plugging better for applying soldermask on via-holes with ENIG?

A: The choice between via tenting and via plugging depends on the specific requirements of your PCB design and manufacturing process. Via tenting is generally simpler and more cost-effective, but may lead to air entrapment and uneven soldermask coverage. Via plugging provides a more stable base for soldermask adhesion but requires an additional process step and may affect the electrical characteristics of the vias. -

Q: How does the aspect ratio of via-holes affect soldermask application?

A: The aspect ratio of via-holes, which is the ratio of the hole depth to its diameter, can significantly impact the ability to achieve even and consistent soldermask coverage. High aspect ratio vias (greater than 8:1) are more challenging to cover uniformly, as the soldermask may have difficulty penetrating deep into the holes. In such cases, via plugging or selective via capping may be necessary to ensure adequate soldermask coverage. -

Q: Can soldermask application on via-holes with ENIG affect the impedance of the PCB?

A: Yes, soldermask application on via-holes can affect the impedance of the PCB, particularly in high-frequency designs. The dielectric constant of the soldermask material, as well as the thickness and uniformity of the coverage, can influence the capacitance and impedance of the vias. It is essential to take these factors into account during the PCB design and manufacturing process to ensure the desired electrical performance. -

Q: How can I test the quality and reliability of soldermask coverage on via-holes with ENIG?

A: There are several methods to test the quality and reliability of soldermask coverage on via-holes with ENIG: -

Visual inspection: Use a microscope to examine the soldermask coverage on the via-holes, looking for any voids, cracks, or areas of exposed copper.

- Cross-sectional analysis: Cut a cross-section of the PCB through the via-holes and examine the soldermask coverage using a microscope. This method provides a detailed view of the soldermask thickness and uniformity.

- Adhesion testing: Perform a tape test or peel test to assess the adhesion of the soldermask to the via-holes. Poor adhesion can indicate compatibility issues or improper surface preparation.

- Thermal cycling: Subject the PCB to thermal cycling tests to evaluate the stability and durability of the soldermask coverage under varying temperature conditions.

- Solderability Testing: Conduct solderability tests to ensure that the soldermask coverage on the via-holes does not interfere with the ability to form reliable solder joints during assembly.

By employing a combination of these testing methods, you can gain a comprehensive understanding of the quality and reliability of the soldermask coverage on your via-holes with ENIG.

Conclusion

Applying soldermask on via-holes in conjunction with the chemical Nickel-Gold surface finish presents unique challenges and considerations for PCB manufacturers. By understanding the benefits and drawbacks of various approaches, such as via tenting, via plugging, and selective via capping, and following best practices for soldermask application and testing, it is possible to achieve reliable and high-quality soldermask coverage on via-holes with ENIG.

As PCB designs continue to push the boundaries of miniaturization and high-frequency performance, the importance of effective soldermask application on via-holes will only continue to grow. By staying informed about the latest technologies, materials, and processes, PCB manufacturers can meet these challenges head-on and deliver products that meet the ever-increasing demands of the electronics industry.

No responses yet