Understanding Metastability in FPGAs

Metastability is a phenomenon that occurs in digital systems when a signal is sampled at the exact moment it is transitioning between two stable states. This can lead to unpredictable behavior and potential system failures. In Field Programmable Gate Arrays (FPGAs), metastability is a significant concern due to the inherent asynchronous nature of the device and the presence of multiple clock domains.

What is Metastability?

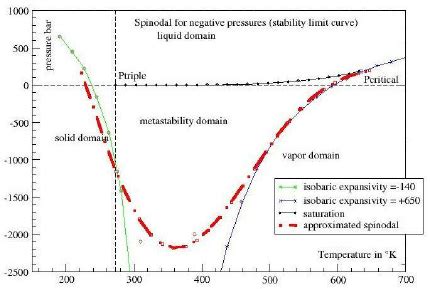

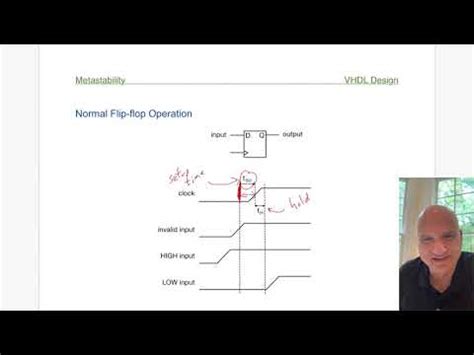

Metastability occurs when a flip-flop or latch enters an unstable state where its output is neither a logical ‘1’ nor a logical ‘0’. This can happen when the setup and hold time requirements of the flip-flop are violated, typically due to asynchronous inputs or clock domain crossings.

| Condition | Result |

|---|---|

| Setup time violation | Metastability |

| Hold time violation | Metastability |

| Asynchronous input | Metastability |

| Clock domain crossing | Metastability |

Impact of Metastability on FPGA Designs

Metastability can cause various issues in FPGA designs, including:

- Unpredictable behavior

- System crashes or lockups

- Data corruption

- Intermittent failures

These issues can be difficult to debug and reproduce, making it crucial to address metastability during the design process.

Techniques for Reducing Metastability

1. Synchronization

One of the most effective ways to reduce metastability in FPGA designs is through proper synchronization techniques. Synchronization involves using flip-flops to sample asynchronous inputs and ensure that the input signal is stable before it is used in the rest of the design.

Double Flip-Flop Synchronizer

The double flip-flop synchronizer is a common technique used to synchronize asynchronous inputs. It consists of two flip-flops connected in series, with the asynchronous input connected to the first flip-flop’s D input and the clock connected to both flip-flops.

module double_ff_sync (

input wire clk,

input wire async_in,

output reg sync_out

);

reg ff1;

always @(posedge clk) begin

ff1 <= async_in;

sync_out <= ff1;

end

endmodule

The first flip-flop samples the asynchronous input, and the second flip-flop samples the output of the first flip-flop. This arrangement allows the metastable state to resolve before the synchronized output is used in the rest of the design.

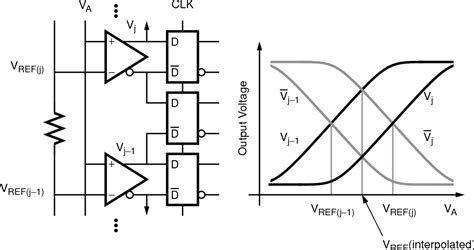

Handshake Synchronization

Handshake synchronization is another technique used to safely transfer data between two clock domains. It involves using a request-acknowledge protocol to ensure that data is transferred only when both the sending and receiving domains are ready.

module handshake_sync (

input wire clk_src,

input wire clk_dest,

input wire [7:0] data_in,

output reg [7:0] data_out,

output reg data_valid

);

reg [7:0] data_ff;

reg req_ff, ack_ff;

// Source domain

always @(posedge clk_src) begin

if (ack_ff == req_ff) begin

data_ff <= data_in;

req_ff <= ~req_ff;

end

end

// Destination domain

always @(posedge clk_dest) begin

ack_ff <= req_ff;

if (ack_ff != req_ff) begin

data_out <= data_ff;

data_valid <= 1;

end else begin

data_valid <= 0;

end

end

endmodule

In this example, the source domain sends a request signal (req_ff) along with the data. The destination domain acknowledges the request by setting ack_ff equal to req_ff. Once the acknowledgment is received, the source domain can send new data.

2. CDC Verification

Clock Domain Crossing (CDC) verification is an essential step in reducing metastability in FPGA designs. CDC verification tools analyze the design and identify potential metastability issues caused by clock domain crossings.

Some popular CDC verification tools include:

- Mentor Graphics Questa CDC

- Cadence Conformal CDC

- Synopsys SpyGlass CDC

These tools help designers identify and fix CDC issues early in the design process, reducing the risk of metastability-related failures.

3. Metastability-Hardened Components

FPGA vendors offer metastability-hardened components that are designed to minimize the impact of metastability. These components include:

- Metastability-hardened flip-flops

- Synchronizers

- Clock domain crossing interfaces

By using these components in your FPGA design, you can reduce the risk of metastability and improve overall system reliability.

4. Timing Constraints

Properly setting timing constraints is crucial for reducing metastability in FPGA designs. Timing constraints help the synthesis and place-and-route tools optimize the design to meet the specified requirements, including setup and hold times.

Some important timing constraints to consider include:

- Clock period

- Clock uncertainty

- False paths

- Multicycle paths

By accurately specifying these constraints, designers can ensure that the FPGA tools generate a design that is less susceptible to metastability.

Best Practices for Reducing Metastability

In addition to the techniques mentioned above, there are several best practices that designers can follow to reduce metastability in their FPGA designs:

-

Minimize the number of clock domains: Reducing the number of clock domains in your design can help minimize the occurrence of clock domain crossings and the associated risk of metastability.

-

Use synchronous design practices: Synchronous design practices, such as using a single clock source and avoiding asynchronous inputs, can help reduce the risk of metastability.

-

Add sufficient timing margin: Providing adequate timing margin for setup and hold times can help minimize the risk of metastability. This can be achieved by adjusting clock periods or adding delay elements.

-

Verify the design thoroughly: Comprehensive verification, including CDC verification and gate-level simulation, can help identify and address potential metastability issues before the design is implemented on an FPGA.

-

Monitor metastability during operation: Implementing metastability monitoring techniques, such as error detection and correction mechanisms, can help identify and mitigate metastability issues during system operation.

FAQ

-

Q: What is the main cause of metastability in FPGA designs?

A: The main cause of metastability in FPGA designs is the violation of setup and hold time requirements, typically due to asynchronous inputs or clock domain crossings. -

Q: How does a double flip-flop synchronizer help reduce metastability?

A: A double flip-flop synchronizer helps reduce metastability by sampling the asynchronous input with the first flip-flop and then sampling the output of the first flip-flop with the second flip-flop. This arrangement allows the metastable state to resolve before the synchronized output is used in the rest of the design. -

Q: What are some popular CDC verification tools?

A: Some popular CDC verification tools include Mentor Graphics Questa CDC, Cadence Conformal CDC, and Synopsys SpyGlass CDC. -

Q: How can timing constraints help reduce metastability in FPGA designs?

A: Properly setting timing constraints, such as clock period, clock uncertainty, false paths, and multicycle paths, can help the synthesis and place-and-route tools optimize the design to meet the specified requirements, including setup and hold times. This can help reduce the risk of metastability in the design. -

Q: What are some best practices for reducing metastability in FPGA designs?

A: Some best practices for reducing metastability in FPGA designs include minimizing the number of clock domains, using synchronous design practices, adding sufficient timing margin, verifying the design thoroughly, and monitoring metastability during operation.

No responses yet