What is a JK Flip Flop?

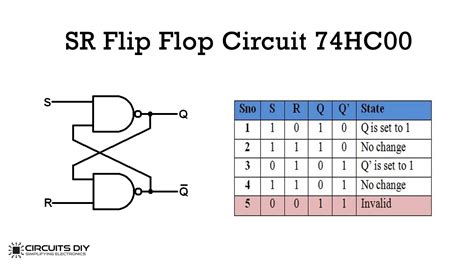

A JK flip flop is a type of sequential logic circuit that has two inputs, traditionally labeled as J (set) and K (reset), and two outputs, Q and its complement Q’. The JK flip flop is a modified version of the SR (Set-Reset) flip flop, with the added advantage of eliminating the invalid or undefined state that occurs when both S and R inputs are simultaneously high.

The JK flip flop operates on the principle of a feedback loop, where the output state depends not only on the current input values but also on the previous output state. This memory effect allows the JK flip flop to store and maintain binary data even after the input signals have been removed.

JK Flip Flop Truth Table

To understand the behavior of a JK flip flop, let’s examine its truth table. The truth table represents the output states (Q and Q’) based on the various combinations of input signals (J and K) and the current output state (Q).

| J | K | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

In the truth table, Q(t) represents the current output state, and Q(t+1) represents the next output state after the input signals have been applied. The behavior of the JK flip flop can be summarized as follows:

- When J=0 and K=0, the output state remains unchanged (Hold state).

- When J=0 and K=1, the output state is reset to 0 (Reset state).

- When J=1 and K=0, the output state is set to 1 (Set state).

- When J=1 and K=1, the output state toggles, i.e., it changes from 0 to 1 or from 1 to 0 (Toggle state).

JK Flip Flop Circuit Diagram

The circuit diagram of a JK flip flop consists of two cross-coupled NAND gates and two AND gates. The NAND gates form the basic latch structure, while the AND gates provide the necessary gating for the J and K inputs.

In the circuit diagram, the J and K inputs are connected to the upper AND gates, while the clock signal (CLK) is connected to the lower AND gates. The outputs of the AND gates are fed into the NAND latch, which determines the output state based on the input signals and the previous output state.

When the clock signal is low, the JK flip flop maintains its current state, regardless of the values of J and K inputs. On the rising edge of the clock signal, the JK flip flop samples the J and K inputs and updates its output state according to the truth table.

Applications of JK Flip Flops

JK flip flops find extensive applications in various digital circuits and systems. Some of the notable applications include:

-

Counters: JK flip flops are commonly used in the design of synchronous and asynchronous counters. By cascading multiple JK flip flops and configuring their J and K inputs appropriately, different types of counters can be implemented, such as binary counters, modulo counters, and ring counters.

-

Shift Registers: JK flip flops are used as the basic building blocks in shift registers, which are digital circuits that can store and shift binary data. Shift registers find applications in serial-to-parallel and parallel-to-serial data conversion, data buffering, and digital delay lines.

-

Frequency Division: JK flip flops can be used to divide the frequency of a clock signal by a factor of 2. By connecting the Q’ output to the J and K inputs, the JK flip flop toggles its state on every clock pulse, effectively dividing the input frequency by 2. This technique is commonly used in clock divider circuits and frequency synthesis.

-

State Machines: JK flip flops are essential components in the design of finite state machines (FSMs). FSMs are sequential logic circuits that transition between different states based on input conditions and generate appropriate output signals. JK flip flops are used to store the current state of the FSM and facilitate state transitions.

-

Synchronization and Debouncing: JK flip flops can be used for synchronizing asynchronous input signals to a clock domain and eliminating metastability issues. They are also employed in switch debouncing circuits to remove the unwanted glitches and bounces that occur when mechanical switches are pressed or released.

Advantages and Disadvantages of JK Flip Flops

Advantages:

- JK flip flops eliminate the invalid state present in SR flip flops, making them more reliable and predictable.

- The toggle feature of JK flip flops allows for easy implementation of frequency division and counter circuits.

- JK flip flops offer a high degree of flexibility and can be used in various digital circuits and applications.

Disadvantages:

- JK flip flops have a slightly more complex circuit structure compared to other types of flip flops, such as D flip flops.

- The presence of two inputs (J and K) increases the number of possible input combinations, which may require additional logic for proper control and management.

Frequently Asked Questions (FAQs)

- What is the difference between a JK flip flop and an SR flip flop?

-

The main difference between a JK flip flop and an SR flip flop lies in their behavior when both inputs are high. In an SR flip flop, setting both S and R inputs to 1 leads to an invalid or undefined state. In contrast, a JK flip flop eliminates this invalid state by toggling its output when both J and K inputs are high.

-

What happens when both J and K inputs are low in a JK flip flop?

-

When both J and K inputs are low (0), the JK flip flop maintains its current output state. This condition is known as the hold state, where the output remains unchanged until the next clock pulse.

-

Can a JK flip flop be used as a T flip flop?

-

Yes, a JK flip flop can be configured to function as a T (toggle) flip flop by connecting the J and K inputs together. When both inputs are high, the JK flip flop toggles its output state on each clock pulse, behaving like a T flip flop.

-

What is the role of the clock signal in a JK flip flop?

-

The clock signal synchronizes the operation of a JK flip flop. The flip flop samples the J and K inputs on the rising edge of the clock signal and updates its output state accordingly. The clock signal ensures that state transitions occur at well-defined time instances, preventing any race conditions or unwanted glitches.

-

How can multiple JK flip flops be connected to create a counter?

- To create a counter using JK flip flops, multiple flip flops are cascaded in a chain, with the output of one flip flop connected to the clock input of the next flip flop. The J and K inputs of each flip flop are configured based on the desired counting sequence. By appropriately connecting the J and K inputs and selecting the initial states, various types of counters can be implemented, such as binary counters, modulo counters, or ring counters.

Conclusion

The JK flip flop is a versatile and widely used sequential logic circuit in digital electronics. Its truth table defines the output states based on the J and K input combinations and the current output state. The circuit diagram of a JK flip flop consists of cross-coupled NAND gates and AND gates, forming a latch structure with gated inputs.

JK flip flops find extensive applications in counters, shift registers, frequency division, state machines, synchronization, and debouncing circuits. They offer advantages such as eliminating the invalid state present in SR flip flops and providing a toggle feature for easy implementation of frequency division and counter circuits.

Understanding the JK flip flop truth table, circuit diagram, and its applications is crucial for anyone involved in digital circuit design and analysis. By mastering the concepts and principles behind JK flip flops, engineers and hobbyists can effectively harness their capabilities to create robust and efficient digital systems.

No responses yet