Introduction to Pseudo-Differential IO

Pseudo-differential IO is a type of input/output standard that combines the benefits of both single-ended and differential signaling. It provides a balanced, noise-resistant transmission method while requiring fewer pins compared to fully differential IO standards. Pseudo-differential IO is widely used in high-speed communication interfaces, such as memory interfaces, serial links, and high-speed buses.

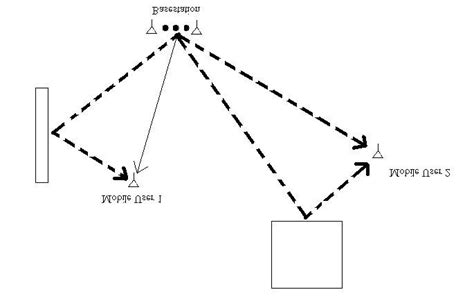

How Pseudo-Differential IO Works

In pseudo-differential IO, a single-ended signal is transmitted along with a reference voltage. The reference voltage is typically set to half the supply voltage (VCC/2) and serves as a common mode reference for the single-ended signal. The receiver compares the single-ended signal with the reference voltage to determine the logic state of the transmitted data.

The key advantages of pseudo-differential IO include:

- Reduced pin count compared to fully differential IO

- Improved noise immunity compared to single-ended IO

- Lower power consumption compared to fully differential IO

- Simplified PCB routing and layout

Pseudo-Differential IO Standards

There are several pseudo-differential IO standards supported by the EP3C40F780C8N FPGA device. These standards differ in their electrical characteristics, such as voltage levels, termination schemes, and data rates. Some of the commonly used pseudo-differential IO standards include:

- LVDS (Low-Voltage Differential Signaling)

- BLVDS (Bus LVDS)

- MLVDS (Multipoint LVDS)

- SLVS (Scalable Low-Voltage Signaling)

- MIPI (Mobile Industry Processor Interface)

- RSDS (Reduced Swing Differential Signaling)

LVDS (Low-Voltage Differential Signaling)

LVDS is a popular pseudo-differential IO standard that offers high-speed data transmission with low power consumption and good noise immunity. It is widely used in applications such as high-speed serial links, display interfaces, and automotive electronics.

LVDS Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 350 mV |

| Common mode voltage | 1.2 V |

| Termination resistor | 100 Ω |

| Maximum data rate | 655 Mbps |

LVDS Implementation on EP3C40F780C8N

The EP3C40F780C8N FPGA supports LVDS IO standard through its dedicated LVDS transmitter and receiver circuits. To implement LVDS on the EP3C40F780C8N, follow these steps:

- Assign the LVDS IO standard to the desired pins using the Quartus II software

- Configure the LVDS transmitter and receiver settings, such as output voltage, pre-emphasis, and equalization

- Ensure proper termination of the LVDS signals using 100 Ω resistors

- Route the LVDS signals on the PCB following the recommended guidelines for differential routing

BLVDS (Bus LVDS)

BLVDS is an extension of the LVDS standard that allows for multi-drop bus configurations. It enables multiple receivers to be connected to a single transmitter, making it suitable for applications such as backplane communication and memory interfaces.

BLVDS Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 350 mV |

| Common mode voltage | 1.2 V |

| Termination resistor | 100 Ω |

| Maximum data rate | 655 Mbps |

BLVDS Implementation on EP3C40F780C8N

Implementing BLVDS on the EP3C40F780C8N is similar to implementing LVDS. The additional considerations for BLVDS include:

- Designing the multi-drop bus topology, ensuring proper termination at each receiver

- Configuring the BLVDS transmitter and receivers with appropriate drive strength and termination settings

- Managing the signal integrity of the multi-drop bus through proper PCB layout and routing techniques

MLVDS (Multipoint LVDS)

MLVDS is another extension of the LVDS standard that supports multi-drop bus configurations. It offers improved signal integrity and longer bus lengths compared to BLVDS.

MLVDS Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 350 mV |

| Common mode voltage | 1.2 V |

| Termination resistor | 100 Ω |

| Maximum data rate | 655 Mbps |

MLVDS Implementation on EP3C40F780C8N

Implementing MLVDS on the EP3C40F780C8N follows a similar process as BLVDS implementation. The key considerations include:

- Designing the multi-drop bus topology with proper termination and signal integrity management

- Configuring the MLVDS transmitter and receivers with appropriate settings

- Ensuring proper PCB layout and routing for optimal signal quality

SLVS (Scalable Low-Voltage Signaling)

SLVS is a pseudo-differential IO standard that offers high-speed data transmission with low power consumption and reduced electromagnetic interference (EMI). It is commonly used in applications such as displays, cameras, and high-speed serial interfaces.

SLVS Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 200 mV |

| Common mode voltage | 0.2 V |

| Termination resistor | 100 Ω |

| Maximum data rate | 1 Gbps |

SLVS Implementation on EP3C40F780C8N

To implement SLVS on the EP3C40F780C8N, follow these steps:

- Assign the SLVS IO standard to the desired pins using the Quartus II software

- Configure the SLVS transmitter and receiver settings, such as output voltage and termination

- Ensure proper termination of the SLVS signals using 100 Ω resistors

- Follow recommended PCB layout and routing guidelines for SLVS signals

MIPI (Mobile Industry Processor Interface)

MIPI is a set of standardized interfaces for mobile and embedded devices. It includes several pseudo-differential IO standards, such as MIPI D-PHY and MIPI M-PHY, which are used for high-speed serial communication in applications like camera interfaces, displays, and storage.

MIPI D-PHY Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 200 mV |

| Common mode voltage | 0.2 V |

| Termination resistor | 100 Ω |

| Maximum data rate | 2.5 Gbps |

MIPI M-PHY Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 100 mV |

| Common mode voltage | 0.1 V |

| Termination resistor | 50 Ω |

| Maximum data rate | 5.8 Gbps |

MIPI Implementation on EP3C40F780C8N

Implementing MIPI interfaces on the EP3C40F780C8N involves the following steps:

- Assign the appropriate MIPI IO standard (D-PHY or M-PHY) to the desired pins

- Configure the MIPI transmitter and receiver settings according to the standard specifications

- Ensure proper termination of the MIPI signals using the specified resistor values

- Follow the recommended PCB layout and routing guidelines for MIPI interfaces

RSDS (Reduced Swing Differential Signaling)

RSDS is a pseudo-differential IO standard that provides high-speed data transmission with reduced voltage swing and power consumption compared to LVDS. It is commonly used in display interfaces and high-speed serial links.

RSDS Electrical Characteristics

| Parameter | Value |

|---|---|

| Differential voltage swing | 200 mV |

| Common mode voltage | 1.2 V |

| Termination resistor | 100 Ω |

| Maximum data rate | 1 Gbps |

RSDS Implementation on EP3C40F780C8N

To implement RSDS on the EP3C40F780C8N, follow these steps:

- Assign the RSDS IO standard to the desired pins using the Quartus II software

- Configure the RSDS transmitter and receiver settings, such as output voltage and termination

- Ensure proper termination of the RSDS signals using 100 Ω resistors

- Follow recommended PCB layout and routing guidelines for RSDS signals

Frequently Asked Questions (FAQ)

-

Q: What is the main advantage of using pseudo-differential IO standards?

A: Pseudo-differential IO standards offer a balance between the benefits of single-ended and fully differential signaling. They provide improved noise immunity and signal integrity compared to single-ended IO while requiring fewer pins than fully differential IO. -

Q: How does pseudo-differential IO differ from fully differential IO?

A: In pseudo-differential IO, a single-ended signal is transmitted along with a reference voltage, and the receiver compares the signal with the reference to determine the logic state. In fully differential IO, two complementary signals are transmitted, and the receiver detects the difference between the two signals. -

Q: Can I use the same termination scheme for all pseudo-differential IO standards?

A: While many pseudo-differential IO standards use 100 Ω termination resistors, some standards may require different termination values. Always refer to the specific standard’s specifications for the recommended termination scheme. -

Q: How do I choose the appropriate pseudo-differential IO standard for my application?

A: The choice of pseudo-differential IO standard depends on factors such as the required data rate, power consumption, noise immunity, and compatibility with other devices in the system. Consider the specific requirements of your application and consult the device documentation to select the most suitable standard. -

Q: Are there any special considerations for PCB layout when using pseudo-differential IO?

A: Yes, proper PCB layout is crucial for maintaining signal integrity in pseudo-differential IO. Follow the recommended guidelines for differential routing, such as maintaining equal trace lengths, minimizing crosstalk, and providing adequate ground referencing. Consult the device documentation and PCB design guidelines for specific recommendations.

Conclusion

Pseudo-differential IO standards offer a robust and efficient solution for high-speed data transmission in various applications. The EP3C40F780C8N FPGA supports several popular pseudo-differential IO standards, including LVDS, BLVDS, MLVDS, SLVS, MIPI, and RSDS. By understanding the electrical characteristics and implementation requirements of each standard, designers can effectively utilize the pseudo-differential IO capabilities of the EP3C40F780C8N to achieve reliable and high-performance communication interfaces.

When implementing pseudo-differential IO on the EP3C40F780C8N, it is essential to follow the recommended design practices, such as proper pin assignment, transmitter and receiver configuration, signal termination, and PCB layout. By adhering to these guidelines and carefully considering the specific requirements of the application, designers can unlock the full potential of pseudo-differential IO and ensure optimal signal integrity and system performance.

No responses yet