Introduction to Flip-Flops

Flip-flops are essential building blocks in digital electronics, used for storing and synchronizing binary data. They are fundamental components in a wide range of applications, including computer memory, counters, shift registers, and control circuits. Flip-flops come in various types, each with its own characteristics and triggering methods. In this article, we will focus on negative edge triggered flip-flops, exploring their functionality, types, and applications.

What are Flip-Flops?

A flip-flop is a digital circuit that has two stable states and can be used to store binary data. It is a bistable multivibrator that can maintain its state indefinitely until directed by an input signal to change its state. Flip-flops are edge-triggered, meaning they change their state only on the rising or falling edge of a clock signal.

Types of Flip-Flops

There are several types of flip-flops, each with its own unique characteristics and applications:

- SR (Set-Reset) Flip-Flop

- D (Data) Flip-Flop

- JK Flip-Flop

- T (Toggle) Flip-Flop

In this article, we will primarily focus on the D flip-flop and its negative edge triggered variant.

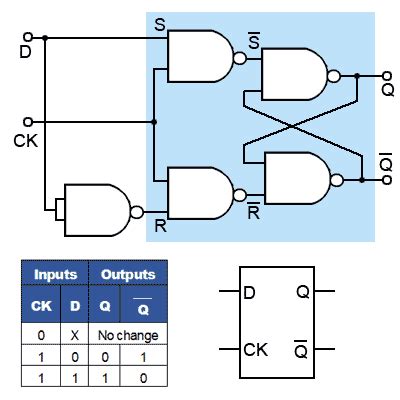

Negative Edge Triggered D Flip-Flop

What is a D Flip-Flop?

A D flip-flop, also known as a data or delay flip-flop, is a digital circuit that captures the value of the D input and stores it in the flip-flop’s output (Q) on the rising or falling edge of the clock signal. The D input can be either a logic ‘0’ or a logic ‘1’, and the flip-flop will store and output this value until the next triggering edge of the clock signal.

Negative Edge Triggering

Negative edge triggering refers to the flip-flop’s ability to change its state on the falling edge (high-to-low transition) of the clock signal. In contrast, positive edge triggering occurs on the rising edge (low-to-high transition) of the clock signal. Negative edge triggered flip-flops are denoted by a bubble on the clock input, indicating that the flip-flop is sensitive to the falling edge of the clock.

Truth Table

The truth table for a negative edge triggered D flip-flop is as follows:

| D | Clock | Q |

|---|---|---|

| 0 | ↓ | 0 |

| 1 | ↓ | 1 |

| X | 1 or 0 | Q |

In this table, ‘X’ represents a “don’t care” condition, meaning the input can be either ‘0’ or ‘1’ without affecting the output. The arrow ‘↓’ represents the falling edge of the clock signal.

Timing Diagram

The timing diagram for a negative edge triggered D flip-flop illustrates the relationship between the D input, clock signal, and Q output:

___________ ___________

Clock | | | |

| |________| |________

___________ ___________

D __| |______________|

_________________

Q ________________| |________

In this diagram, the Q output changes state only on the falling edge of the clock signal, capturing and storing the value of the D input.

Characteristic Equation

The characteristic equation for a negative edge triggered D flip-flop is:

Q(next) = D

This equation indicates that the next state of the flip-flop’s output (Q) is equal to the current value of the D input.

Applications of Negative Edge Triggered D Flip-Flops

Shift Registers

Negative edge triggered D flip-flops are commonly used in shift registers, which are digital circuits that can store and shift binary data. Shift registers are used in various applications, such as:

- Serial-to-parallel data conversion

- Parallel-to-serial data conversion

- Temporary data storage

- Delay lines

In a shift register, multiple D flip-flops are connected in a chain, with the output of one flip-flop connected to the input of the next. The data is shifted through the register on each falling edge of the clock signal.

Counters

Counters are digital circuits that keep track of the number of occurrences of an event or the number of clock cycles that have elapsed. Negative edge triggered D flip-flops can be used to construct various types of counters, including:

- Asynchronous (ripple) counters

- Synchronous counters

- Up/down counters

- Modulo counters

In a counter, the flip-flops are connected in a specific arrangement, with the output of one flip-flop influencing the input of the next. The falling edge of the clock signal triggers the flip-flops to change state, incrementing or decrementing the counter’s value.

Frequency Division

Negative edge triggered D flip-flops can be used to divide the frequency of a clock signal by a factor of 2. This is achieved by connecting the inverted output (Q’) of the flip-flop to its D input. On each falling edge of the clock signal, the flip-flop will toggle its state, resulting in an output frequency that is half of the input clock frequency.

Frequency division is useful in various applications, such as:

- Generating lower-frequency clock signals from a higher-frequency source

- Reducing power consumption in digital systems

- Avoiding timing violations in high-speed circuits

Synchronization

Negative edge triggered D flip-flops are often used for synchronizing asynchronous signals in digital systems. Asynchronous signals are those that are not synchronized with the system clock and can cause metastability issues if not properly handled.

By using a negative edge triggered D flip-flop, an asynchronous signal can be synchronized to the falling edge of the clock, ensuring that the signal is stable and valid when it is captured by the flip-flop. This technique is known as double-edge synchronization and is commonly used in asynchronous-to-synchronous interfaces.

Advantages and Disadvantages

Advantages of Negative Edge Triggered D Flip-Flops

-

Synchronization: Negative edge triggered flip-flops allow for the synchronization of asynchronous signals to the falling edge of the clock, minimizing metastability issues.

-

Timing margins: Using negative edge triggering can provide additional timing margins in digital systems, as the falling edge of the clock typically occurs later than the rising edge.

-

Power reduction: In some cases, negative edge triggering can help reduce power consumption by allowing for more time for signals to settle before being captured by the flip-flop.

Disadvantages of Negative Edge Triggered D Flip-Flops

-

Compatibility: Negative edge triggered flip-flops may not be compatible with all digital systems, as some systems are designed to work exclusively with positive edge triggered components.

-

Design complexity: Incorporating negative edge triggered flip-flops into a digital design may increase the overall complexity, as designers must consider the timing relationships between the falling edges of the clock and the data signals.

Frequently Asked Questions (FAQ)

- What is the difference between a positive and negative edge triggered flip-flop?

-

A positive edge triggered flip-flop changes its state on the rising edge (low-to-high transition) of the clock signal, while a negative edge triggered flip-flop changes its state on the falling edge (high-to-low transition) of the clock signal.

-

Can a negative edge triggered D flip-flop be used in place of a positive edge triggered one?

-

In some cases, yes, but it depends on the specific requirements of the digital system. It is essential to consider factors such as timing margins, signal integrity, and compatibility with other components when making this decision.

-

How does a negative edge triggered D flip-flop synchronize asynchronous signals?

-

A negative edge triggered D flip-flop can synchronize an asynchronous signal by capturing the signal’s value on the falling edge of the clock. This ensures that the signal is stable and valid when it is stored in the flip-flop’s output.

-

What is the characteristic equation for a negative edge triggered D flip-flop?

-

The characteristic equation for a negative edge triggered D flip-flop is Q(next) = D, which means that the next state of the flip-flop’s output (Q) is equal to the current value of the D input.

-

What are some common applications of negative edge triggered D flip-flops?

- Negative edge triggered D flip-flops are commonly used in applications such as shift registers, counters, frequency division, and synchronization of asynchronous signals in digital systems.

Conclusion

Negative edge triggered flip-flops are essential components in digital electronics, offering unique capabilities for storing and synchronizing binary data. By triggering on the falling edge of the clock signal, these flip-flops provide designers with additional options for managing timing relationships and synchronizing asynchronous signals in digital systems.

Understanding the functionality, types, and applications of negative edge triggered flip-flops is crucial for anyone working with digital circuits. Whether you are designing shift registers, counters, or asynchronous-to-synchronous interfaces, negative edge triggered D flip-flops can be a valuable tool in your digital design toolkit.

As with any digital component, it is essential to consider the specific requirements and constraints of your system when deciding whether to use negative edge triggered flip-flops. By carefully analyzing factors such as timing margins, power consumption, and compatibility, you can make informed decisions that optimize the performance and reliability of your digital designs.

No responses yet