Introduction to the 74LS93 IC

The 74LS93 is a popular integrated circuit (IC) used in digital electronics for building Timer Circuits. It is a 4-bit binary counter with a divide-by-2 and divide-by-8 output. The IC is part of the 74LS series, which is a family of low-power Schottky TTL (Transistor-Transistor Logic) devices.

In this comprehensive guide, we will explore the 74LS93 Pinout, its functionality, and how to use it to build timer circuits. We will also cover some practical examples and frequently asked questions to help you better understand this versatile IC.

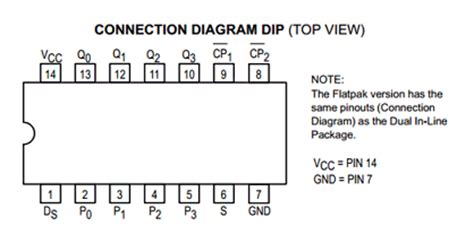

Understanding the 74LS93 Pinout

To effectively use the 74LS93 IC, it is essential to understand its pinout. The 74LS93 comes in a 14-pin Dual In-Line Package (DIP). Here’s a table showing the pin configuration:

| Pin Number | Pin Name | Description |

|---|---|---|

| 1 | QA | Output A |

| 2 | QB | Output B |

| 3 | QC | Output C |

| 4 | QD | Output D |

| 5 | Gnd | Ground |

| 6 | CP0 | Clock Pulse 0 Input |

| 7 | MR1 | Master Reset 1 Input |

| 8 | MR2 | Master Reset 2 Input |

| 9 | Vcc | Power Supply |

| 10 | CP1 | Clock Pulse 1 Input |

| 11 | Q2 | Divide-by-2 Output |

| 12 | NC | No Connection |

| 13 | NC | No Connection |

| 14 | Q8 | Divide-by-8 Output |

Inputs and Outputs

The 74LS93 has two clock pulse inputs (CP0 and CP1) and two master reset inputs (MR1 and MR2). These inputs control the operation of the counter.

The IC also has four outputs (QA, QB, QC, and QD) that represent the binary count value. Additionally, there are two special outputs: Q2 (divide-by-2) and Q8 (divide-by-8), which provide divided-down versions of the input clock signal.

Power Supply and Ground

Pin 9 (Vcc) is the power supply pin, which should be connected to a +5V DC source. Pin 5 (Gnd) is the ground pin, which should be connected to the common ground of the circuit.

How the 74LS93 Works

The 74LS93 is a 4-bit binary counter that increments its count value on each rising edge of the clock pulse input. The counter can be reset to zero by asserting either of the master reset inputs (MR1 or MR2).

Binary Counting

The outputs QA, QB, QC, and QD represent the binary count value. Each output corresponds to a bit in the 4-bit binary number, with QA being the least significant bit (LSB) and QD being the most significant bit (MSB).

For example, if the counter’s current value is 1010 (binary), the output states would be:

– QA = 0

– QB = 1

– QC = 0

– QD = 1

Divide-by-2 and Divide-by-8 Outputs

The Q2 and Q8 outputs provide divided-down versions of the input clock signal. The Q2 output toggles its state on every rising edge of the clock pulse, effectively dividing the input frequency by 2. The Q8 output toggles its state every 8 clock pulses, dividing the input frequency by 8.

These outputs are useful for generating lower frequency signals or for cascading multiple 74LS93 ICs to create larger counters.

Building Timer Circuits with the 74LS93

The 74LS93 is commonly used to build timer circuits. By combining the IC with other components such as resistors, capacitors, and oscillators, you can create various timing functions.

Basic Timer Circuit

Here’s an example of a basic timer circuit using the 74LS93:

+5V

|

+-+

| |

| |

| | R1

| | 10K

| |

+-+

|

|

+--+--+

| 1 |

CP0 | | Vcc

| |

MR1 | | CP1

| |

MR2 |74 | Q2

|LS93 |

QD | | QC

| |

QA | | QB

| |

Gnd | | Q8

+-----+

|

===

GND

In this circuit, the 74LS93 is connected to a 10K resistor (R1) and a +5V power supply. The CP0 and CP1 inputs are tied together and connected to an oscillator or clock source. The MR1 and MR2 inputs are grounded to keep the counter enabled.

The Q2 and Q8 outputs can be used to generate divided-down clock signals, while the QA, QB, QC, and QD outputs provide the binary count value.

Adjustable Timer Circuit

To create an adjustable timer circuit, you can add a potentiometer to control the input clock frequency:

+5V

|

+-+

| |

| |

| | R1

| | 10K

| |

+-+

|

|

+-+

| |

| | RV1

| | 100K

| |

+-+

|

|

+--+--+

| 1 |

CP0 | | Vcc

| |

MR1 | | CP1

| |

MR2 |74 | Q2

|LS93 |

QD | | QC

| |

QA | | QB

| |

Gnd | | Q8

+-----+

|

===

GND

In this circuit, a 100K potentiometer (RV1) is added to control the input clock frequency. By adjusting the potentiometer, you can change the timing period of the circuit.

Frequently Asked Questions (FAQ)

-

Q: What is the maximum clock frequency that the 74LS93 can handle?

A: The maximum clock frequency for the 74LS93 is typically around 25MHz, but it can vary depending on the specific manufacturer and operating conditions. -

Q: Can I cascade multiple 74LS93 ICs to create a larger counter?

A: Yes, you can cascade multiple 74LS93 ICs by connecting the Q8 output of one IC to the CP0 input of the next IC. This allows you to create counters with a higher number of bits. -

Q: How do I reset the counter to zero?

A: To reset the counter to zero, you need to assert either the MR1 or MR2 input. This can be done by applying a logic high signal to the respective pin. -

Q: What is the purpose of the divide-by-2 and divide-by-8 outputs?

A: The divide-by-2 (Q2) and divide-by-8 (Q8) outputs provide divided-down versions of the input clock signal. They are useful for generating lower frequency signals or for cascading multiple 74LS93 ICs. -

Q: Can I use the 74LS93 with a 3.3V power supply?

A: No, the 74LS93 is designed to operate with a 5V power supply. Using a lower voltage may result in incorrect operation or damage to the IC.

Conclusion

The 74LS93 is a versatile 4-bit binary counter IC that finds applications in various timer circuits. By understanding its pinout and functionality, you can effectively use the 74LS93 to build custom timing solutions for your projects.

In this guide, we covered the basics of the 74LS93, including its pin configuration, inputs, outputs, and operating principles. We also provided examples of basic and adjustable timer circuits using the 74LS93.

Remember to consider factors such as the maximum clock frequency, power supply requirements, and cascading options when designing your circuits. With the knowledge gained from this guide, you should be well-equipped to incorporate the 74LS93 into your timer circuit projects.

No responses yet