Introduction to the 74LS74

The 74LS74 is a dual D-type positive-edge-triggered flip-flop with preset and clear inputs. It is part of the 7400 series of transistor-transistor logic (TTL) integrated circuits used in a wide variety of digital systems. This versatile chip finds applications in counters, registers, frequency dividers, data latches, and various other digital circuits.

Key Features of the 74LS74

- Dual D-type positive-edge-triggered flip-flops

- Preset and clear inputs for each flip-flop

- Operating frequency up to 45 MHz

- Low power consumption: 4.4 mA per flip-flop

- Wide operating voltage range: 4.75 V to 5.25 V

- High noise immunity

- Available in various packages: DIP, SOIC, TSSOP

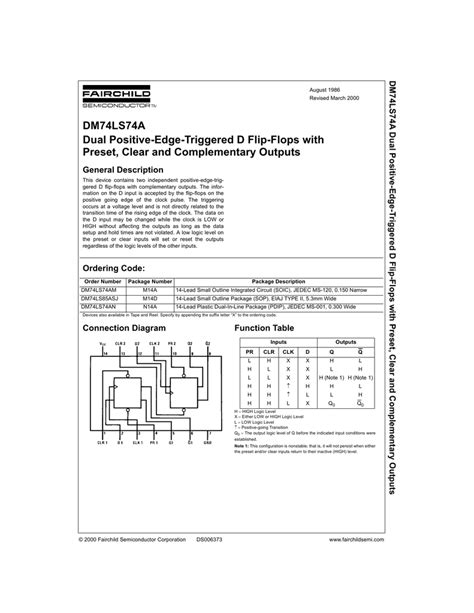

Understanding the 74LS74 Pin Configuration

The 74LS74 comes in a 14-pin dual in-line package (DIP) or surface-mount packages such as SOIC and TSSOP. The pin configuration for the DIP package is as follows:

| Pin | Name | Description |

|---|---|---|

| 1 | CLR1 | Clear input for flip-flop 1 |

| 2 | D1 | Data input for flip-flop 1 |

| 3 | CLK1 | Clock input for flip-flop 1 |

| 4 | PRE1 | Preset input for flip-flop 1 |

| 5 | Q1 | Output of flip-flop 1 |

| 6 | ~Q1 | Inverted output of flip-flop 1 |

| 7 | GND | Ground |

| 8 | ~Q2 | Inverted output of flip-flop 2 |

| 9 | Q2 | Output of flip-flop 2 |

| 10 | PRE2 | Preset input for flip-flop 2 |

| 11 | CLK2 | Clock input for flip-flop 2 |

| 12 | D2 | Data input for flip-flop 2 |

| 13 | CLR2 | Clear input for flip-flop 2 |

| 14 | VCC | Power supply (5 V) |

How the 74LS74 Flip-flops Work

The 74LS74 contains two independent D-type flip-flops. Each flip-flop has a data input (D), clock input (CLK), preset input (PRE), clear input (CLR), and outputs Q and ~Q (inverted Q).

D-type Flip-flop Operation

A D-type flip-flop captures the state of the D input at the rising edge of the clock signal and holds that state until the next rising edge. The truth table for a D-type flip-flop is as follows:

| D | CLK | Q (next state) |

|---|---|---|

| 0 | Rising edge | 0 |

| 1 | Rising edge | 1 |

| X | No rising edge | Q (no change) |

Preset and Clear Inputs

The preset (PRE) and clear (CLR) inputs are active-low asynchronous inputs that override the normal flip-flop operation. When PRE is low, the flip-flop output Q is forced high (1), and when CLR is low, the output Q is forced low (0). If both PRE and CLR are low simultaneously, the output state is undefined.

Timing Characteristics of the 74LS74

Understanding the timing characteristics of the 74LS74 is crucial for proper circuit design and operation. Some key timing parameters include:

- Setup time (tsu): The minimum time the D input must be stable before the rising edge of the clock for reliable data capture. Typically 20 ns for the 74LS74.

- Hold time (th): The minimum time the D input must remain stable after the rising edge of the clock for reliable data capture. Typically 5 ns for the 74LS74.

- Propagation delay (tpd): The time taken for the output to change state after the rising edge of the clock. Typically 22 ns for the 74LS74.

- Maximum clock frequency: The highest frequency at which the flip-flop can reliably operate. For the 74LS74, this is about 45 MHz.

Applications of the 74LS74

The 74LS74 finds use in a wide range of digital circuits, including:

Frequency Dividers

By connecting the ~Q output to the D input, the 74LS74 can function as a divide-by-2 frequency divider. Each flip-flop will toggle its state on every rising edge of the clock, effectively dividing the input frequency by 2.

Data Latches

The 74LS74 can be used as a data latch to capture and hold data from a bus or other source. The D input is connected to the data source, and the clock input is used to control when the data is captured.

Shift Registers

Multiple 74LS74 flip-flops can be cascaded to form a shift register. The Q output of each flip-flop is connected to the D input of the next, and data is shifted through the register on each clock cycle.

Counters

The 74LS74 can be used as a building block for various types of counters, such as binary counters, Johnson counters, and ring counters. By combining multiple flip-flops and appropriate feedback logic, a wide range of counting functions can be implemented.

Interfacing with the 74LS74

When designing circuits using the 74LS74, consider the following:

- Ensure proper power supply decoupling with ceramic capacitors close to the VCC and GND pins to minimize noise and prevent erratic operation.

- Use appropriate pull-up or pull-down resistors on unused inputs to prevent floating inputs and unwanted oscillations.

- Be mindful of the timing requirements, such as setup and hold times, to ensure reliable data capture and avoid metastability issues.

- Consider the fan-out of the 74LS74 outputs, as each output can drive a limited number of inputs depending on the connected device’s input characteristics.

Frequently Asked Questions (FAQ)

1. What is the difference between the 74LS74 and other 74 series flip-flops?

The 74LS74 is a low-power Schottky TTL device, offering improved speed and power consumption compared to the standard 7474. Other variants, such as the 74HC74 and 74HCT74, use CMOS technology for even lower power consumption and wider voltage ranges.

2. Can the 74LS74 be used in 3.3 V systems?

While the 74LS74 is designed for 5 V operation, it may work in 3.3 V systems with reduced noise margin and performance. For 3.3 V systems, it is recommended to use devices specifically designed for that voltage, such as the 74LVC74 or 74HC74.

3. How do I create a reset signal for the 74LS74?

To create a reset signal, connect the CLR input to a logic circuit that generates a low pulse when a reset is desired. This can be done using a simple RC network, a dedicated reset IC, or a microcontroller output.

4. What is the purpose of the preset input on the 74LS74?

The preset input allows you to force the flip-flop output to a known state (high) independently of the clock and data inputs. This is useful for initializing the flip-flop to a specific state at power-up or during a reset sequence.

5. Can I replace a 74LS74 with a different flip-flop IC?

In many cases, yes, but it is important to ensure that the replacement device has compatible pin assignments, voltage levels, and timing characteristics. Always consult the datasheets of both devices to verify compatibility.

Conclusion

The 74LS74 dual D-type flip-flop is a versatile and widely used component in digital electronics. Its ability to capture, store, and synchronize data makes it an essential building block in a wide range of applications, from simple data latches to complex state machines and digital control systems.

By understanding the pin configuration, operation, timing characteristics, and application examples provided in this comprehensive guide, you can effectively integrate the 74LS74 into your digital designs and harness its potential for reliable and efficient data handling.

As with any digital component, proper design practices, such as power supply decoupling, pull-up/down resistors, and timing considerations, are crucial for optimal performance and reliability. By following these guidelines and leveraging the 74LS74’s features, you can create robust and sophisticated digital circuits that meet your application’s requirements.

No responses yet